超大规模集成电路设计自动化

清华大学计算机系 EDA 研究室成立于 70 年代初,在电子设计自动化理论、算法及系统研究方面有长期的研究历史。在高层次综合、验证和模拟,互连线规划与优化,时钟网络设计优化,电源 / 地线网络设计优化,布图规化,布局,布线和寄生参数提取等方面进行深入研究,积累了大量的研究成果和经验。在全面和系统研究的基础上形成了自己独特的研究 体系和方法。其研究成果连续在国际设计自动化年会( DAC )、国际计算机辅助设计年会( ICCAD )、国际物理设计年会( ISPD )和亚太地区设计自动化年会( ASP-DAC )等国际学术会议上发表论文 30 多篇。

近年来取得多项科研成果:

- 完成国内首个国家自然科学基金中美双方在信息领域重大国际合作项目:“ 系统级芯片的设计方法及其 EDA 关键技术研究。” 项目对系统芯片 SOC 设计方法和 EDA 技术进行了实质性的合作研究,取得国际领先的突破性成果。基金委组织的验收专家认为该项目“在一些关键技术上取得国际领先水平的突破性进展,我国学者已经能够站在 EDA 技术研究的国际前沿。”

- 完成了“ 863 ”项目“基于超深亚微米物理级优化 SOC CAD 技术”,获得 2007 年北京市科学技术二等奖。

- 完成了“ 973 ”项目“ 超大规模集成电路设计中 NP-Hard 问题与高性能软件研究”, 获得 2005 年度教育部自然科学二等奖。

- 参加“ 973 ”项目“高效率的处理芯片设计、验证与测试”,成果发表在 DAC07 国际会议上。

- 在布图规划算法 方面,提出的角模块表示方法成为国际上布图表示流派之一。 成果发表在 DAC 、 ICCAD 等国际会议上。

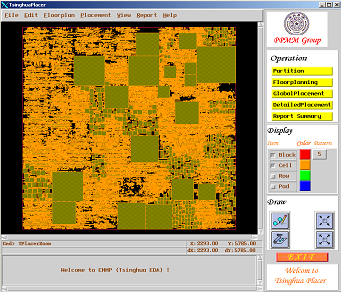

- 在布局方面,与 Intel 公司进行国际合作,开发了混合模式的布局算法和工具,交付 Intel 公司,对方给予的评价为“世界一流水平”。

- 在三维芯片设计方面,与 Intel 公司进行国际合作,开发三维芯片布图规划与布局算法和工具,成果发表在 ISPD06 国际会议上,并被 2005 年 ASICON 国际会议评为最佳论文。

- 在低功耗时钟和布局优化方面,提出了一系列优化算法和策略,成果发表在 DAC05 、 ISPD07 等国际会议上,并被 2008 年 GLSVLSI 国际会议评为最佳论文。

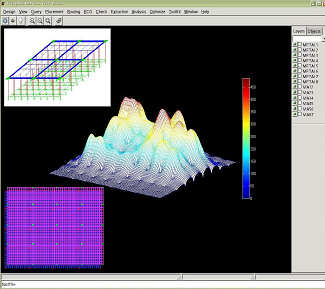

- 研究开发了片上电源 / 地线网络静态和瞬态分析、优化算法和工具,成果发表在 IEEE Transactions on CAD 国际期刊以及 ICCAD 、 ISPD 等国际会议上。算法的核心部分用于美国 CELESTRY 公司合作的产品中。

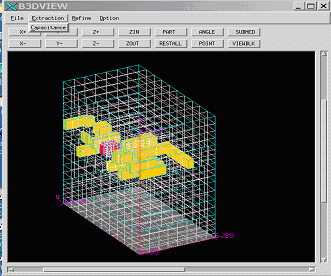

- 研究开发了电阻、电感、电容三维寄生参数提取算法和工具,与美国 Synopsys 公司、日本精工电子公司等进行国际合作,成果发表在 IEEE Transactions on CAD 、 IEEE Transaction on MTT 等国际期刊上。